We’ve got an exciting opportunity to collaborate on a new research project in our group. See the details here.

We’ve got an exciting opportunity to collaborate on a new research project in our group. See the details here.

I’m very excited to be the new Editor-in-Chief of the IEEE Solid-State Circuits Letters (SSC-L)!

SSC-L publishes short papers on novel integrated circuit (IC) ideas and experimental results with a faster turnaround than its sister publication, the Journal of Solid-State Circuits. Prof. Behzad Razavi was the publication’s founding Editor-in-Chief. Over the past three years, he assembled a distinguished editorial board and editorial review board and oversaw the publication’s steady growth. We should all be grateful for his service to the community.

I now look forward to working with SSC-L’s outstanding volunteers to build on the publication’s unique strengths as a venue for IC research. Our ability to publish a peer-reviewed paper to a worldwide audience within three months of submission is tremendously valuable to many authors. Likewise, readers trying to stay abreast of our fast-moving field benefit from a constant stream of the latest results. I hope to raise awareness of these strengths while maintaining our high-quality peer-review process on a fast turnaround. Doing so will accelerate progress on significant IC research problems and facilitate the rapid translation of research results into tangible benefits for all of humanity.

I’m chairing a forum on Optical and Electrical Transceivers for 400GbE and Beyond at this year’s International Solid-State Circuits Conference. Eight 45-minute forum presentations from experts in industry and academia go live on February 12. We’ll then have a live Q&A with the presenters on February 22. Register for the conference to get access at isscc.org.

I’m looking for an accomplished researcher to help lead our efforts on high-speed optoelectronic computing and communication. As a post-doctoral fellow, you’d have the unique opportunity to collaborate across disciplines and sectors (academia & industry) on a well-resourced project in an emerging field. If you’re interested in joining us and have a background in IC design and/or integrated photonics, please send your CV to contact@isl.utoronto.ca within the next 10 days.

I’m looking for an accomplished researcher to help lead our efforts on high-speed optoelectronic computing and communication. As a post-doctoral fellow, you’d have the unique opportunity to collaborate across disciplines and sectors (academia & industry) on a well-resourced project in an emerging field. If you’re interested in joining us and have a background in IC design and/or integrated photonics, please send your CV to contact@isl.utoronto.ca within the next 10 days.

Prof. Chan Carusone presented at the Open Compute Platform’s Virtual Summit on Friday, May 15 describing our work towards Intelligent Interconnect. The presentation is posted on YouTube.

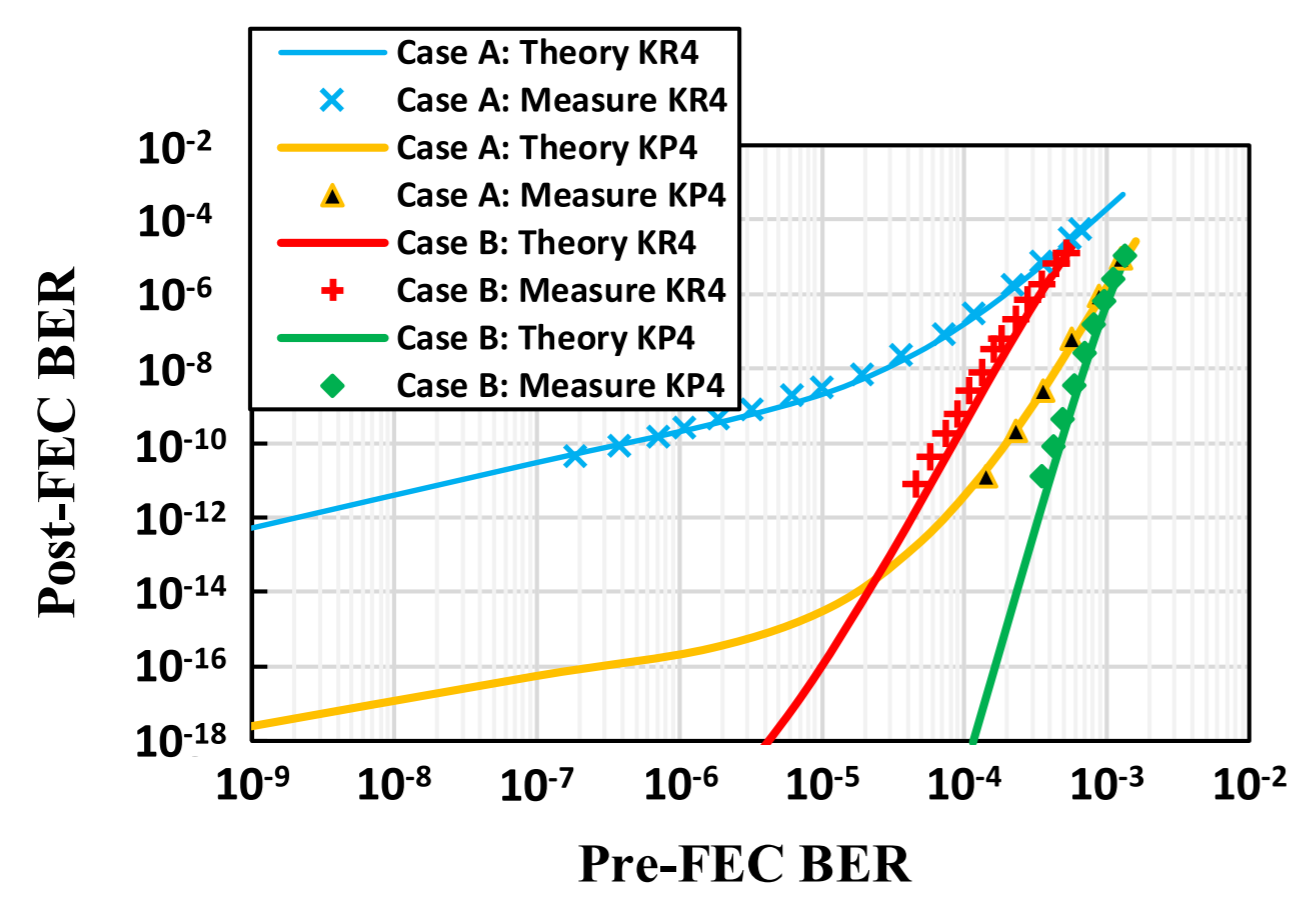

Simulations to accurately predict error probabilities below 10-15 in communication links with forward error correction used to take 1000’s years on a typical desktop. Ph.D. Candidate Ming Yang has developed techniques that allow us to do it in under a minute. With the help of our industry partners, the techniques have been validated on real wireline links at 60 Gbps. If you missed him present the techniques at DesignCon in Santa Clara, January 2020, then read about it in our recently-published open-access paper.

Simulations to accurately predict error probabilities below 10-15 in communication links with forward error correction used to take 1000’s years on a typical desktop. Ph.D. Candidate Ming Yang has developed techniques that allow us to do it in under a minute. With the help of our industry partners, the techniques have been validated on real wireline links at 60 Gbps. If you missed him present the techniques at DesignCon in Santa Clara, January 2020, then read about it in our recently-published open-access paper.

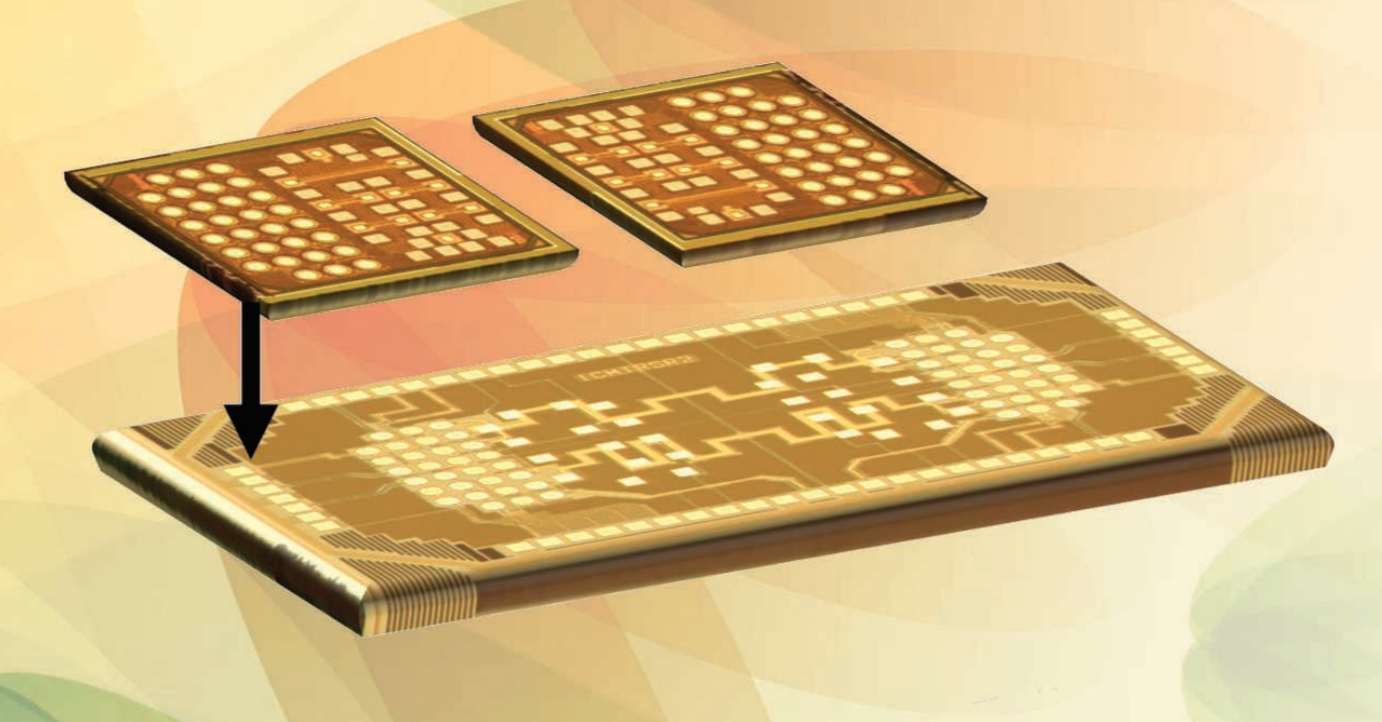

Check out our article in the IEEE Solid-State Circuits Magazine. We overview die-to-die interconnect technology that has paved the way for chiplets and is revolutionizing high-performance computing and networking systems.

Check out our article in the IEEE Solid-State Circuits Magazine. We overview die-to-die interconnect technology that has paved the way for chiplets and is revolutionizing high-performance computing and networking systems.

Two ISL alumni presented back-to-back to a packed crowd of over 400 researchers at the ISSCC 2019 session on “Advanced Wireline Techniques” Wednesday afternoon, February 20th in San Francisco: congratulations to Shayan Shahramian and Masum Hossain. In total, six ISL alumni were authors on ISSCC papers this year.

Two ISL alumni presented back-to-back to a packed crowd of over 400 researchers at the ISSCC 2019 session on “Advanced Wireline Techniques” Wednesday afternoon, February 20th in San Francisco: congratulations to Shayan Shahramian and Masum Hossain. In total, six ISL alumni were authors on ISSCC papers this year.

In partnership with CMC Microsystems, a very successful workshop on Advanced CMOS technologies was held here at U of T, December 6 & 7, 2018. The event was sold out, with industry and academic attendees from across the country. Prof. Chan Carusone presented the opening remarks and moderated the closing panel session.

In partnership with CMC Microsystems, a very successful workshop on Advanced CMOS technologies was held here at U of T, December 6 & 7, 2018. The event was sold out, with industry and academic attendees from across the country. Prof. Chan Carusone presented the opening remarks and moderated the closing panel session.

Prof. Chan Carusone delivered seminars in Melbourne and Sydney, Australia on CMOS Optical Transceiver circuits, March 15 and 28th, 2018.