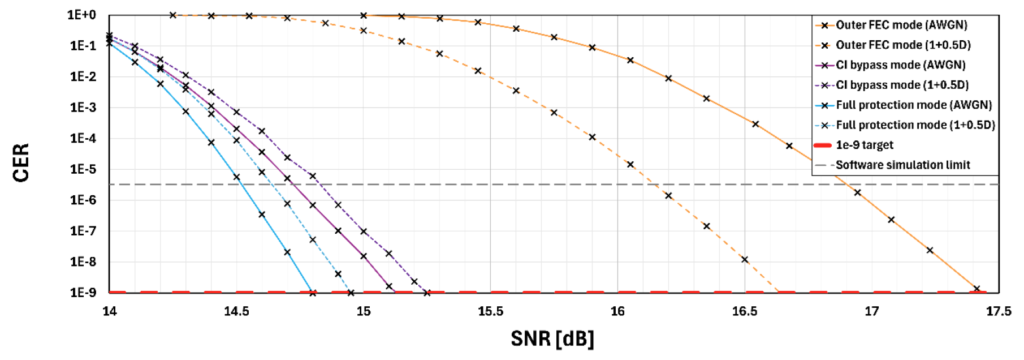

ISL research has again been recognized with a Best Paper Award at DesignCon. This is the third time in five years, an amazing accomplishment considering DesignCon is the premier high-speed communications and system design conference for chip, board, and systems design engineers. The paper is titled “Post-FEC BER Analysis of 200 Gb/s Wireline Systems using an FPGA Platform,” and furthers their past work on evaluating and ensuring post-FEC BER performance for increasingly complex interleaved wireline links with concatenated and interleaved coding. This is a pressing challenge in 200+Gbps wireline links, and promises to be even more so at higher speeds.